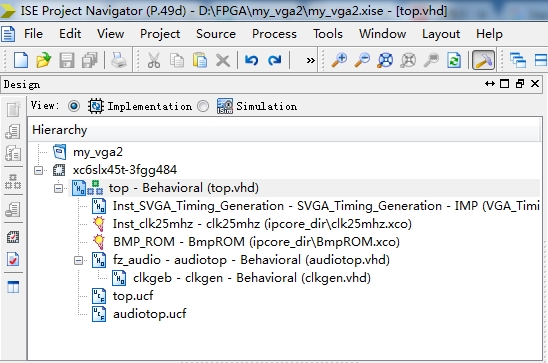

我在做接口实验的时候,想把音频和视频的两个接口合在一起,核心思想是,在视频的工程里,把音频作为组件引入,把端口对应上,就可以了。不过过程却没那么顺利。

我使用的是Xilinx ISE 14.4,使用VHDL语言对FPGA进行编程,实现对接口的控制。

当我把两个模块组合起来之后,却发现无法通过综合,报错ERROR:Xst:2035 - Port <clk> has illegal connections. This port is connected to an input buffer and other components.。由于我对硬件知识掌握不够,不太能看懂字面意思,搜索了报错信息,找到了两篇比较有价值的:这个和这个。大致意思就是:我把一个buffer端口作为输出不经任何电路直接赋给另外一个端口,让它直接用这个值,这个做法是不对的。因为这样会存在buffer的分支被短路的可能。

但是我的电路里的时钟clk并不是buffer类型的呀?!文章中说ISE会根据需要产生buffer,给出的解决方法是关闭这个自动产生buffer的功能。但是这样其实是不对的,因为没有解决根本问题,ISE产生buffer肯定是有意义的,不会无缘无故产生,即使你关闭了这个功能,肯定还会有其他错误产生。事实上确实是这样。关闭Add I/O Buffers之后,综合倒是通过了,实现的时候报错了:ERROR:NgdBuild:924 - input pad net 'clk' is driving non-buffer primitives:。

所以说还是要解决根本问题,找一找代码中哪究竟是哪里产生了buffer。

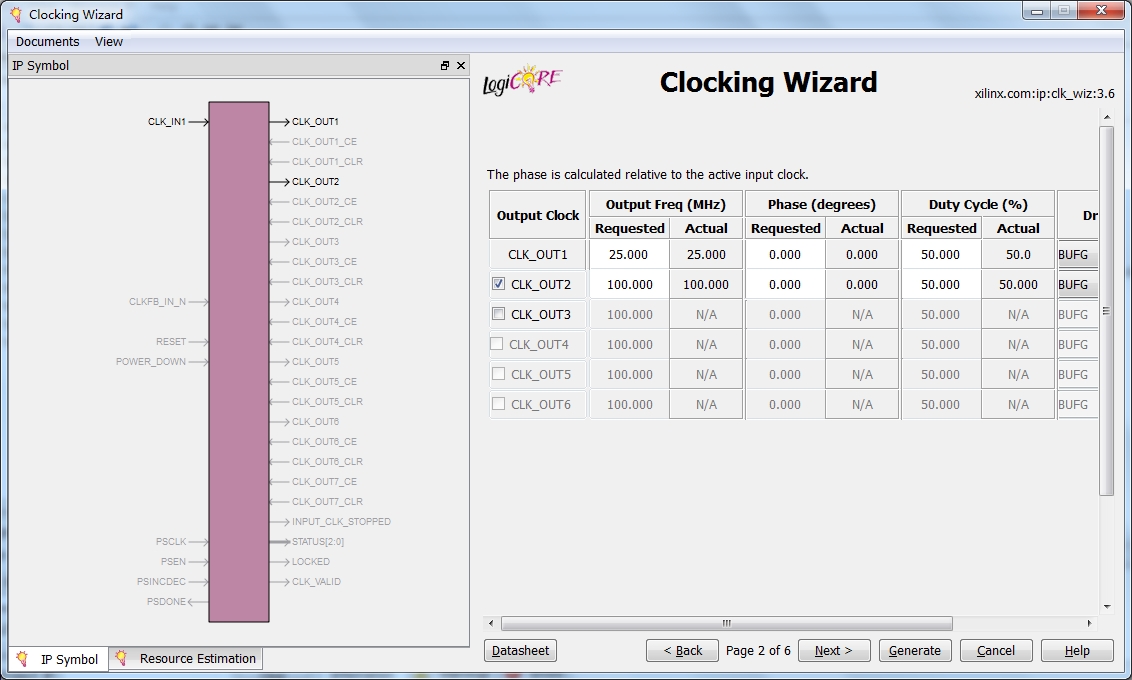

我找了很久,终于找到了问题的关键所在。我的视频模块使用了ISE自带的IP Core——一个由100MHz时钟产生25MHz时钟的一个时钟发生器。这个时钟发生器将clk板上时钟读入(CLK_IN1),产生一个25MHz的时钟输出(CLK_OUT1),而这个读入是有buffer的,所以在经过这个模块之后,板上时钟clk已经不能被直接读入了。

在了解了这一点之后,我们很容易想到一个解决方法:让这个时钟发生器再产生一个100MHz的时钟,给音频模块用,不就解决了吗?!

使用这个新输出的时钟之后,问题解决!

另外提一下,Xilinx ISE 14.4不支持Win10。

欢迎留言